# 高信頼微細へテロ接合バイポーラトランジスタ技術

## ~次世代フォトニックネットワークを支える電気回路の基盤技術~

### どんな問題に取り組むのか?

私たちは、超100Gbit/s級光通信用電子回路実現を目的に、高周波動作に優れたInP系へテロ接合バイポーラトランジスタを開発してきました。しかしながら、そのような高速動作では通電時間とともに電流利得が著しく劣化し、信頼性が確保できないという問題がありました。

#### 得られた結果はどう新しいのか?

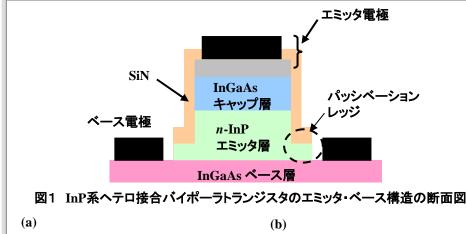

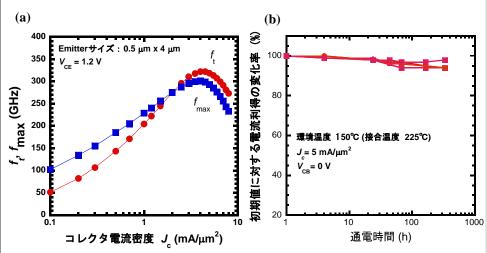

エピタキシャル層を薄層化、エミッタ幅を0.5μmに微細化することによって、電流利得遮断周波数321GHzを達成しました。更に、パッシベーションレッジ構造と高融点エミッタ電極の導入によって、高いコレクタ電流密度(Jc=5mA/μm²)動作においても電流利得の劣化を抑制できることが明らかになりました。

### ての研究が成功した場合のインパクトは?

今回開発したトランジスタ技術により、高速と信頼性を兼ね備えたトランジスタの実現が可能になりました。今後は、信頼性を備えた超100Gbit/s級電子回路の実現を目指します。

連絡先: NTTフォトニクス研究所 テラビットデバイス研究部

柏尾 典秀 (KASHIO NORIHIDE) 、栗島 賢二(KURISHIMA KENJI)、

深井 佳乃(FUKAI YOSHINO)、山幡 章司(YAMAHATA SHOJI)

TEL: 046-240-2240 FAX: 046-240-3261 電子メール: kashio@aecl.ntt.co.jp

図2 (a) 電流利得遮断周波数f<sub>t</sub>及び最大発信周波数f<sub>max</sub>のコレクタ電流密度依存性

(b) 通電時間に対する電流利得の変化率